| |

|

|

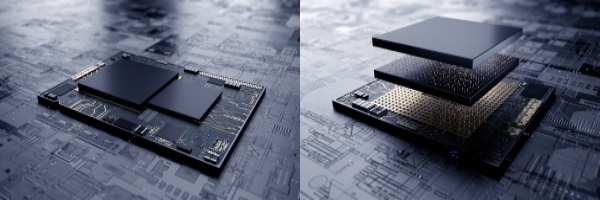

| ▲ 기존 시스템반도체의 평면 설계(왼쪽)과 삼성 3차원 적층 기술 'X-Cube'를 적용한 시스템반도체의 설계. /사진=삼성전자 제공 |

[미디어펜=권가림 기자] 삼성전자는 업계 최초로 7나노 EUV(극자외선) 시스템반도체에 3차원 적층 패키지 기술을 적용했다고 13일 밝혔다.

삼성전자는 3차원 적층 패키지 기술인 'X-Cube'를 적용한 테스트칩 생산에 성공했다. 이 기술은 전공정을 마친 웨이퍼 상태인 칩 여러 개를 위로 얇게 쌓아서 하나의 반도체를 만드는 기술이다.

시스템반도체는 일반적으로는 CPU(중앙처리장치)·GPU(그래픽처리장치)·NPU(신경망처리장치) 등 역할을 하는 로직 부분과 캐시 메모리 역할을 하는 에스램 부분을 하나의 칩에 평면(2차원)으로 나란히 배치·설계한다.

칩을 평면이 아닌 위로 여러층 적층하면 단위 면적당 저장 용량을 극대화할 수 있어 반도체 업체들은 고성능 시스템반도체 수요 증가에 대응한 3차원 적층 기술 개발에 주력하고 있다.

삼성전자가 EUV 시스템반도체에 3차원 적층 패키지 기술을 처음으로 적용하며 파운드리 분야에서 앞선 행보를 나타낸 것이다.

'X-Cube' 기술은 로직과 에스램을 단독으로 설계해서 위로 적층하면서 전체 칩 면적을 줄인다. 이에 따라 고용량 메모리 솔루션을 장착할 수 있어 고객의 설계 자유도를 높일 수 있다.

또 실리콘관통전극 기술을 통해 시스템반도체의 데이터 처리 속도를 향상시키고 전력 효율도 높일 수 있다.

이외에 위아래 칩의 데이터 통신 채널을 고객 설계에 따라 자유자재로 확장하고 데이터 처리 속도를 극대화할 수 있다는 장점도 있다.

이 기술은 슈퍼컴퓨터·인공지능·5G 등 고성능 시스템 반도체를 요구하는 분야는 물론 스마트폰과 웨어러블 기기의 경쟁력을 높일 수 있는 핵심 기술로 활용될 것으로 예상된다.

반도체 설계회사 팹리스 고객은 삼성전자가 제공하는 'X-Cube' 설계 방법론을 활용해 EUV 기술 기반 5나노, 7나노 공정 칩 개발을 바로 시작할 수 있다.

특히 이미 검증된 삼성전자의 양산 인프라를 이용할 수 있기 때문에 칩 개발 기간을 줄일 수 있다.

삼성전자는 최첨단 EUV 초미세 전공정뿐 아니라 후공정에서도 첨단 기술력을 확보함으로써 오는 2030년까지 시스템 반도체 분야 1위를 달성한다는 목표인 '반도체 비전 2030'에도 큰 역할을 할 것으로 기대했다.

강문수 파운드리사업부 전무는 "EUV 장비가 적용된 첨단 공정에서도 TSV 기술을 안정적으로 구현했다"며 "반도체 성능 한계를 극복하기 위한 기술 혁신을 이어가겠다"고 말했다.

삼성전자는 오는 16일∼18일 온라인으로 열리는 고성능 반도체 관련 연례 학술 행사인 '핫 칩스(Hot Chips) 2020'에서 'X-Cube'의 기술 성과를 공개한다.

[미디어펜=권가림 기자]

▶다른기사보기